FLIP-FLOP merupakan suatu rangkaian yang terdiri sdari dua elemen aktif (Transistor) yang kerjanya saling bergantian. Fungsinya adalah sebagai berikut:

1. Menyimpan bilangan biner

2. Mencacah pulsa

3. Menyerampakkan/men-sinkronkan rangkaian aritmatika

Misalnya : Beberapa full yang dapat dikendalikan

FLIP-FLOP bersifat bistable : dua kondisi yang stabil 0 atau 1. Kondisi ini akan tetap stabil tidak akan berubah jika tidak ada pemicu (input) yang masuk.

Jenis-jenis FLIP-FLOP :

1. RS Flip-flop (Set-Reset Flip-Flop)

FLIP-FLOP RS merupakan rangkaian dasar untuk menyusun berbagai jenis Flip-Flop yang lainnya FLIP-FLOP SR dapat disusun dari dua gerbang NAND atau dua gerbang NOR. Berikut ini karakteristik tabelnya :

| S | R | Q | Ǭ |

| 0 | 0 | Race | Race |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | Tetap | tetap |

Skema Pengkabelan :

2. CLOCK SR FLIP-FLOP

RS FLIP-FLOP dengan clock merupakan pengembangan dari RS FLIP-FLOP dengan menambahkan dua gerbang NAND pada RS FLIP-FLOP dari gerbang Nand dan gerbang AND pada RS FLIP-FLOP dari Gerbang NOR yang bertujuan untuk memasukan pemicu yang disebut dengan sinyal Clock untuk mengubah nilai yang ada.

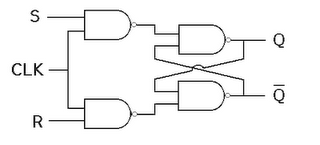

Rangkaian Clock RS FLIP-FLOP:

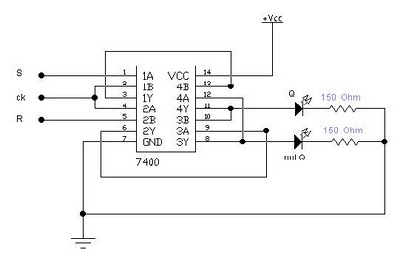

Skema Pengkabelan :

3. D FLIP-FLOP (Delay Flip-Flo)

D Flip-Flop memiliki 1 input yang disebut D (Data) serta 2 output yang disebut Q dan Q. Pada dasarnya D lip-flop diperoleh dari SR flip-flop yang salah satu inputnya didapat dengan mengkomplemenkan input yang lain yaitu menambahkan satu gerbang NOT pada masukan.

Prinsip kerja dari D Flip-flop adalah berapapun nilai yang diberikan pada input D akan dikeluarkan dengan nilai yang sama pada output Q. D Flip-Flop diaplikasikan pada rangkaian-rangkaian yang memerlukan penyimpanan data sementara sebelum diprosesberikutnya. Salah satu contoh IC D Flip-flop adalah 74LS75, yang mempunya input Asinkron.

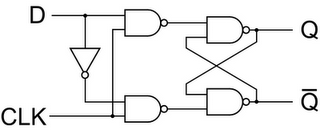

Rangkaian D Flip-Flop:

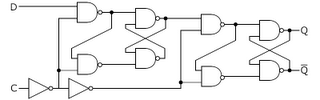

4. Master Slave D Flip-Flop

Master Save D Flip-flop merupakan rangkaian flip-flop yang memiliki 2 latch D dan sebuah inverter. Latch yang satu bernama Master dan yang kedua bernama Slave. Master D hanya akan mendeskripsikan diktat yang outputnya hanya dapt diganti selama ujung negatif jam.

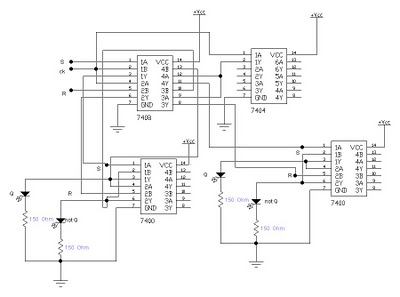

Rangkaian Master Slave D Flip-flop :

5. JK Flip-Flop

Kelemahan dari flip-flop SR adalah munculnya output yang tidak dapat didefinisikan ketika input S dan R tinggi untuk jenis NOR dan rendah untuk jenis AND. Untuk menanggulangi keadaan tersebut, maka dikembangkan menjadi flip-flop JK yang dibangun utnuk mengantisipasi keadaan terlarang pada SR flip-flop.

MASTER SLAVE JK FLIP FLOP

Sebuah master slave JK Flip Flop di bentuk dari dua buah SR Flip Flop, dimana operasi dari kedua SR Flip Flop tersebut dilakukan secara bergantian, dengan memberi input Clock yang berlawanan pada ke dua SR Flip Flop tersebut. Prinsip dasar dari Master Slave JK adalah: jika Clock diberi input “1”, gerbang AND 1 dan 2 akan aktif, SR Flip Flop ke 1 akan menerima data yang di masukkan melalui input Jdan K, semantara gerbang AND 3 dan 4 tidak aktif, sehingga SR Flip Flop ke 2 tidak ada respon. Sebaliknya jika Clock dari input 0, gerbang 3 dan 4 aktif, slave akan mengeluarkan output di Q dan Q’, sementara master tidak merespon input, karena gerbang AND 1 dan 2 tidak aktif.

skema perkabelan :

Rangkaian JK Flip-Flop:

Skema Pengkabelan :

Tidak ada komentar:

Posting Komentar